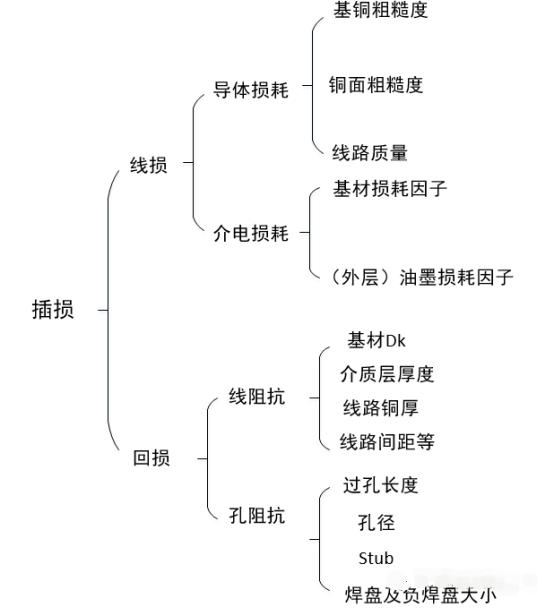

前段实践和客户一起开发一个高速背板项目,客户损耗冗余空间十分有限,要求PCB插损在小于0.5dB@12.89GHz。这是一个非常高的要求,对材料和加工都有很高的要求,因此在做正式项目之前,和客户一起商讨先进行实际插损测试,看选型材料是否能满足要求,再决定下一步的动作。现在这个测试已经做完了,正在和客户探讨下一步的工作。因此想在这分享一些测试结论。当然,基于商业性保密原则,我会刻意隐藏可能涉及商业保密条款的内容。在这里,先从加工角度谈一谈我对PCB插损的理解,对于无组件的传输线模型而言,去除辐射等设计因素影响外,传输线的插损主要包含两个部分,即线损与回损。这里用一个思维导图来表示:

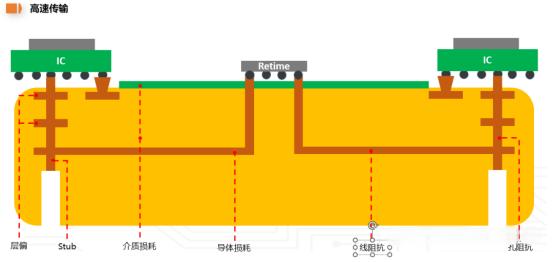

用更加清晰明了的传输模型可以表征损耗在PCB加工端的主要因素(孔阻抗在加工端的主要影响因素为层偏与Stub)为:

综上,PCB加工端需要重点考虑以上对损耗的相关影响因素。具体的加工控制细节放在后面找时间再专门阐述。今天主要想分享这次材料测试相关的内容。

这次测试采用的是Detal-L3.0插损测试方法,它的原理是基于时域反射(TDR)技术,利用电信号在电缆中传输过程中的反射现象来评估插损。它测量并分析信号在电缆中的传输损耗,从而确定插损的大小。它设计有两条不同长度传输线,通过计算不同长度传输线插损值得差异来计算传输线的单位长度损耗,这种方法可以尽可能的消除测试夹具及接触发射对损耗测试的影响,同时能消除阻抗不匹配的影响,因此可以将这里测到的插损即为线损。繁琐的测试过程这里并不详细叙述,仅分享几个重要的结论:1. 当采用M7N级别+HVLP3的铜箔时,采用常规的加工工艺6.5mil线宽6.5mil介厚的差分传输线线损约为0.5-0.55dB/inch;2. 当采用低粗化药水处理带状线铜面时,能使铜表面Rz由常规2-5um将为约1.2um,比表面积由常规50%降为<20%,从而可以将相同设计的损耗降低约10%@12.89GHz。3.当采用旋转拼板,设计0°、5°、13°时,并未发现损耗随着角度变化有规律变化。